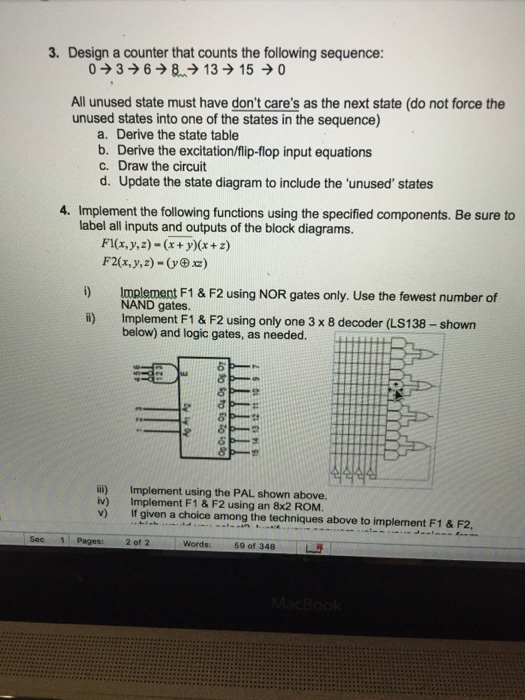

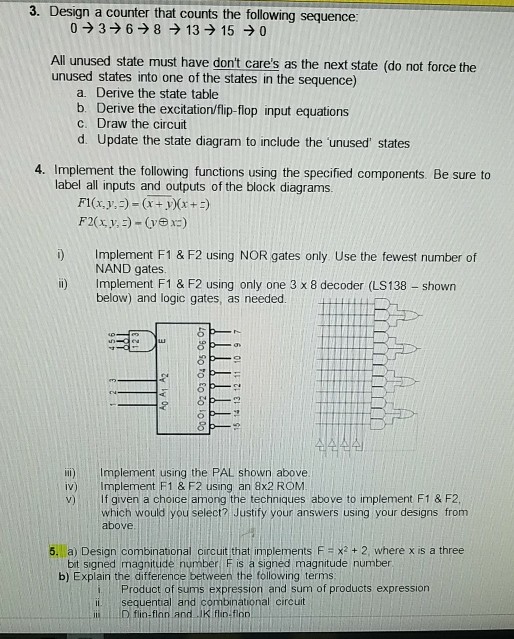

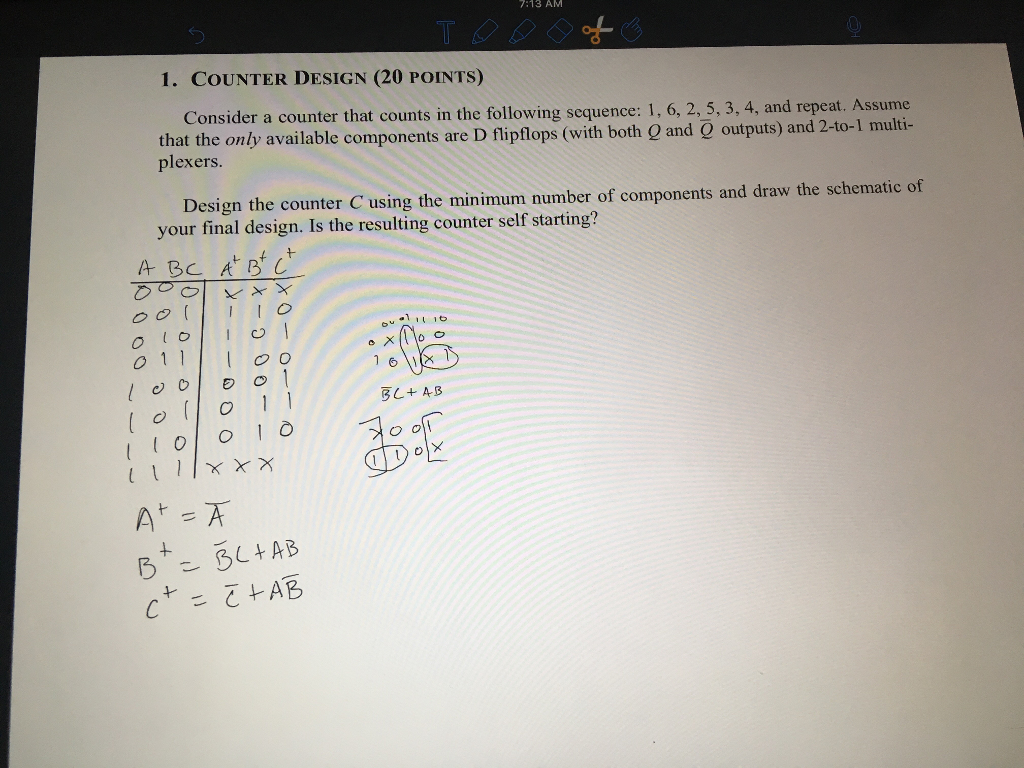

1c using D flip flops. Design a counter with the following repeated binary sequence.

Solved Design A Counter That Counts The Following Sequence Chegg Com

Choose the type of flip flop.

. Since the highest state is 6 ie. Here we see that the least significant bit Q0 of the output never changes so we can either use a D flip-flop with its data D input tied LOW or we could just replace it with a wire tied low. Since it is a 3-bit counter the number of flip-flops required is three.

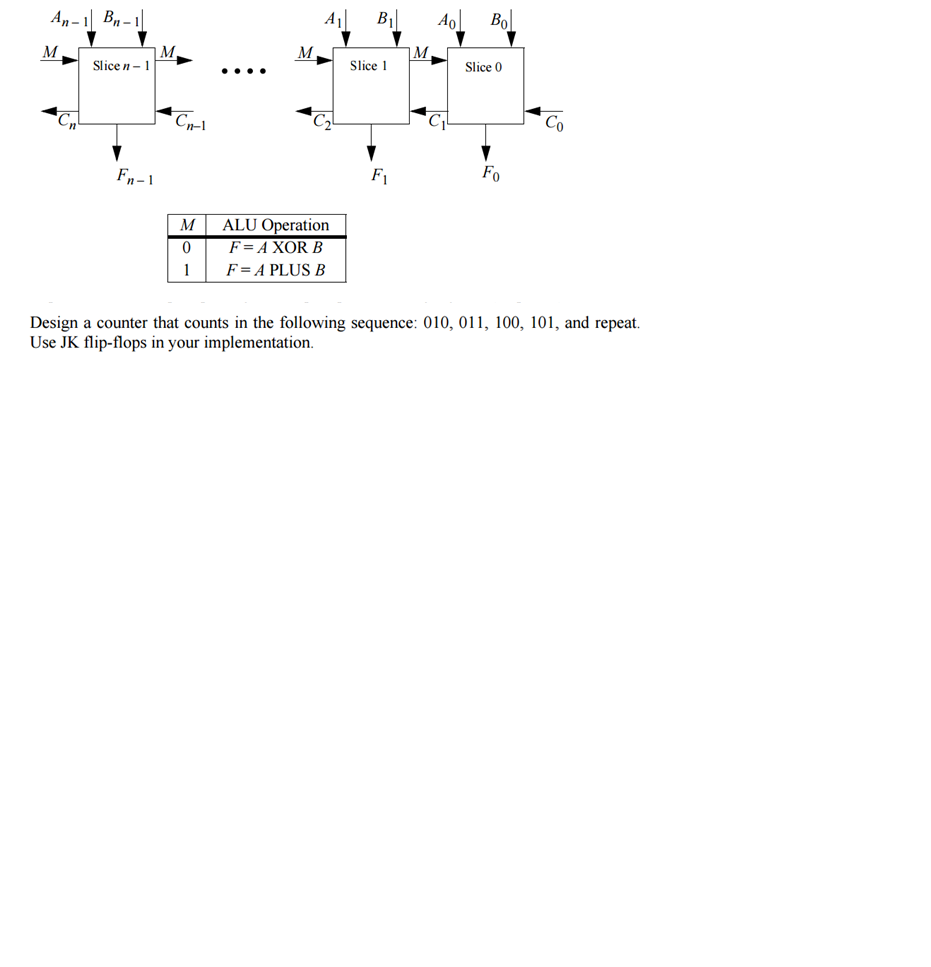

Let us choose JK flip-flops to design the counter. Show that when binary states 010 an. Use a two bit counter.

Electrical Engineering questions and answers. Connect the two Q terminals to outputs 1 and 2. B Design a digital circuit using D flip flops and minimum circuit components.

Draw state diagram for the counter. Design a counter that counts the following sequence of 2-3-1-0 and repeat. Modify your design in question 1a so that the circuit works according to the following function table.

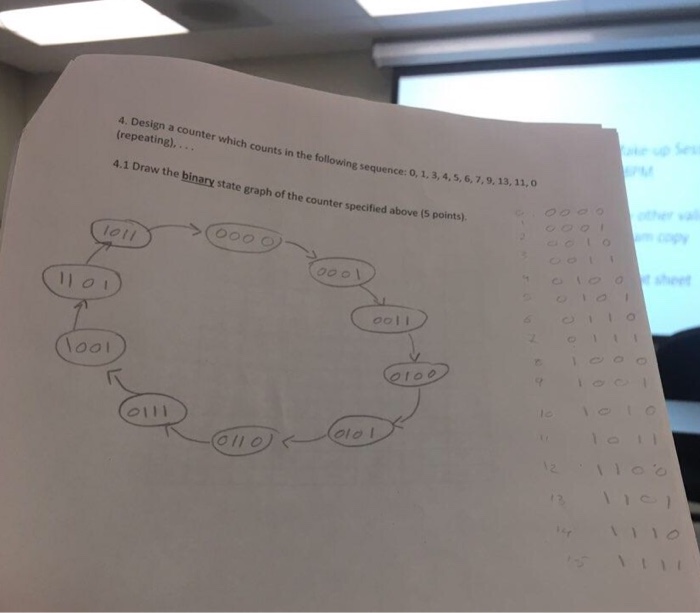

Draw the state diagram. Use JK flip-flops given to you at the start of the semester. Design a counter with the following binary sequence 0 1 3 7 6 4 and represent using T flip flop.

This is a constant logical 0. Design a counter that counts the following sequence. Connect Q1 to clock 2.

Write the excitation table. Written 52 years ago by akamitkhareak 370. 0 4 2 1 6.

Explanation For given sequence state transition diagram as following below. Design a counter with the following repeated binary sequence. 0100 1111 1110 1010 1011 11010110 0010 0111 0011 0101 0000 0001 1100 1000 1001 after that it goes back to 0100 a Make the next state table for this counter.

The count sequence is 7-3-1-2-5-4-6. 011 we have to use three T flip flops. The truth table of a modulus six.

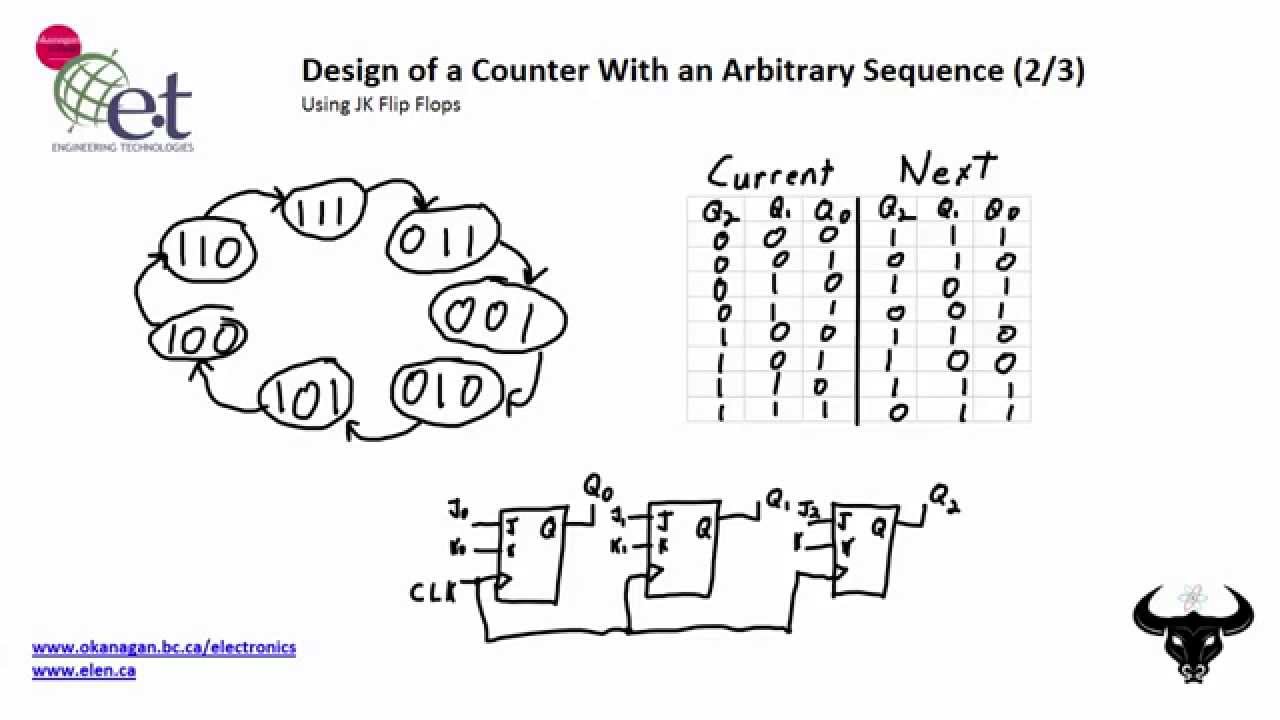

This video is the first of three videos showing how to design a counter with an arbitrary sequence using JK flip flops. Engineering Electrical Engineering QA Library bläi 9 Q11To design a counter which count in the following sequence 763501 by using SR- FF the input of SR-FFs are SAABCABC RA. 1b using T flip flops.

0100 0110 0010 0111 0011 0101 0000 0001 1100 1111 1110 1010 1011 1101 1000 1001 after that it goes back to 0100 a Make the next state table for this counter. Design a counter that counts the following sequence. To design a counter which count in the following sequence 01357 by using T-FF the input of T-FFs are.

These values will be displayed on a seven-segment display like the one used in Lab 3. B Design a digital circuit using D flip flops and minimum circuit components show complete working of Kmaps. Let the type of flip-flops be RS flip-flops.

Videos you watch may be added to. D2 Q2 XOR Q1. This modulus six counter requires three SR flip-flops for the design.

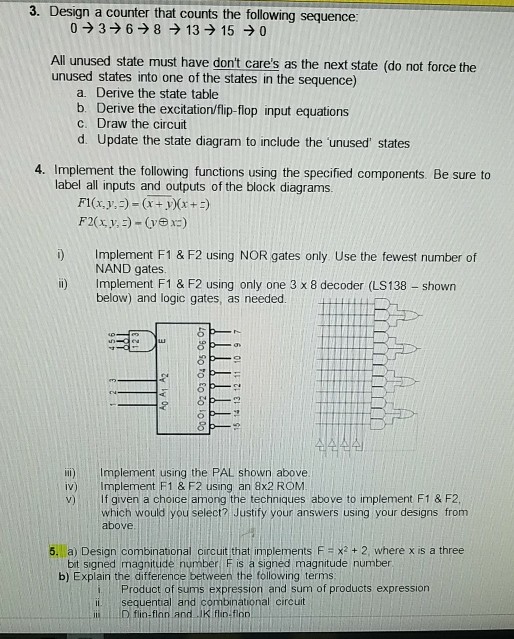

Problem Design synchronous counter for sequence. 0 1 3 7 6 4. Table1 shows the excitation table for T flip flop.

Design a counter with T flipflops that goes through the following binary repeated se- quence. 1a using JK flip flops. 943 Design of a Synchronous Modulus-Six Counter Using SR Flip-Flop The modulus six counter will count 0 2 3 6 5 and 1 and repeat the sequence.

If playback doesnt begin shortly try restarting your device. The other two flip-flops simply form a two-bit binary counter. This video is the first of three videos showing how to design a counter with an arbitrary sequence using JK flip flops.

Mod counter with less than 2n states can be constructed by allowing the counter to skip states that are not required. Number of flip flops. Using JK flip flop.

Hence the counter to be designed will have 3 flip-flops. You dont use the 1 bit. Let the three flip-flops be A B and C.

Connect the clock input to Clock 1. Mod-6 synchronous counter can count from 000 to 101 and on next clock pulse it returns back to initial state ie. 0 1 2 3 4 5 6.

Solution for Design an Asynchronous counter to count the following sequence using T FF. 0 1 3 4 5 7 0 using T flip-flop. Table2 shows the circuit excitation table.

The given count sequence has 3 bits and there are 6 seven states. The count sequence is 7-3-1-2-5-4-6. How do you design a three-bit counter that counts in the sequence 0 2 4 6 0.

The state table is as shown in Table 31. Connect J and K inputs to logical 1. Design a counter which counts 0 4 8 2 6 and repeats using.

Design of synchronous mod-6.

Design A Counter For The Following Binary Sequence 0 4 5 3 1 6 2 7 And Repeat Use Jk Flip Flops Iiit Hyderbad Gate Overflow For Gate Cse

Solved Consider A Counter That Counts In The Following Chegg Com

Solved Design A Counter That Counts In The Following Chegg Com

Design A Counter With An Arbitrary Sequence 2 3 Youtube

Design Counter For Given Sequence Geeksforgeeks

Design Counter For Given Sequence Geeksforgeeks

Solved 4 Design A Counter Which Counts In The Following Chegg Com

Solved 3 Design A Counter That Counts The Following Chegg Com

0 comments

Post a Comment